## **ORIGINAL ARTICLE**

# Channel thickness dependency of high-k gate dielectric based double-gate CMOS inverter

Shubham Tayal<sup>1\*</sup>, Pachimatla Samrat<sup>1</sup>, Vadula Keerthi<sup>1</sup>, Beemanpally Vandana<sup>2</sup>, Shikhar Gupta<sup>3</sup>

Department of ECE, Ashoka Institute of Engineering and Technology, Hyderabad, Telangana, India

Department of ECE, K. G. Reddy College of Engineering and Technology, Hyderabad, Telangana, India

Department of Electronics and Communication Engineering, NIT Kurukshetra, Haryana, India

Received 01 May 2020; revised 20 May 2020; accepted 12 June 2020; available online 20 June 2020

#### Abstract

This work investigates the channel thickness dependency of high-k gate dielectric-based complementary metal-oxide-semiconductor (CMOS) inverter circuit built using a conventional double-gate metal gate oxide semiconductor field-effect transistor (DG-MOSFET). It is espied that the use of high-k dielectric as a gate oxide in n/p DG-MOSFET based CMOS inverter results in a high noise margin as well as gain. It is also found that delay performance of the inverter circuit also gets upgraded slightly by using high-k gate dielectric materials. Further, it is observed that the scaling down of channel thickness ( $T_{si}$ ) improves the noise margin (NM), and gain (A) at the cost of propagation delay ( $P_{d}$ ). Moreover, it is also observed that the changes in noise margin ( $\Delta$ NM = NM $_{(K=40)}$  – NM $_{(K=3.9)}$ ), propagation delay ( $\Delta$ P $_{d}$  =  $P_{d (K=40)}$  –  $P_{d (K=3.9)}$ ), and gain ( $\Delta$ A =  $A_{(K=40)}$  –  $A_{(K=3.9)}$ ) gets hinder at lower  $T_{si}$ . Therefore, it is apposite to look at lower channel thickness (~6 nm) while designing high-k gate dielectric-based DG-MOSFET for CMOS inverter cell.

Keywords: Channel Thickness; CMOS; Double-Gate; High-k Dielectric; Inverter Cell.

## How to cite this article

Tayal Sh., Samrat P., Keerthi V., Vandana B., Gupta Sh. Channel thickness dependency of high-k gate dielectric based double-gate CMOS inverter . Int. J. Nano Dimens., 2020; 11 (3): 215-221.

## **INTRODUCTION**

performance improvement Integrated circuits made a successful demand in semiconductor industries. This is achieved due to the continuous scaling of the semiconductor device which has been reached into the nanometer regime. Due to aggressive scaling of the device dimensions various short channel effects (SCEs) are in the limelight. In contrast to this, the multi-gate architecture is an effective approach owing more channels controllability which condenses SCEs as per reported literature [1-4]. In accordance with the device performance various hybrid topologies like a double gate (DG), triple gate, gate all around (multi-gate) MOSFETs were invented to reduce the SCEs.

Further, to follow the prediction of

international technology roadmap for semiconductor (ITRS), [5] recent research elaborates several device engineering schemes to enhance the performance of scaled devices with minimizing SCEs & maintaining the electrical characteristics constant. By this, the integration level of nano-electronic devices is enhancing linearly. However, the gate oxide layer silicon dioxide (SiO<sub>2</sub>) is decreased to a few nanometer thicknesses thereby maintaining the device performance constant. If the thickness is scaled below 1 nm, quantum tunneling effects are the serious issues that dominate and arise problems in power consumption [6-8]. Technically these issues are overcome by owning high dielectric materials (high-k). The key merit preferring high-k materials for Nano-devices is that the thickness of the high-k dielectric materials increases with the same

<sup>\*</sup> Corresponding Author Email: drtshubham@qmail.com

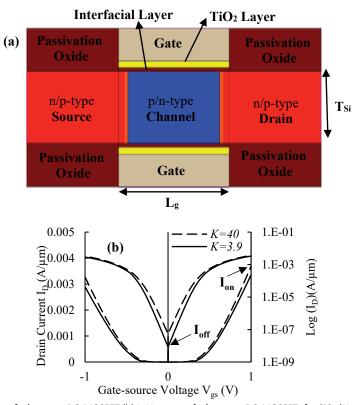

Fig. 1 (a) schematic view of n/p – type DG-MOSFET (b)  $I_p-V_{gs}$  curve of n/p – type DG-MOSFETs for SiO<sub>2</sub> (K = 3.9) and TiO<sub>2</sub> (K = 40).

capacitance. High-*k* dielectric materials induce a larger bandgap and larger dielectric constant. With this prominence, high-*k* materials are well suitable to improvise the device characteristics [9-11].

In this paper, the design of the double gate (DG) MOSFET has been used to investigate the effect of high-k gate dielectric on the digital performance of the complementary metal-oxide-semiconductor (CMOS) inverter circuit. The performance is analyzed in terms of propagation delay (Pa), inverter gain (A), low noise margin (NM,), and high noise margin (NM<sub>H</sub>) of a single-stage CMOS inverter circuit. Furthermore, the dependency of digital performance of high-k gate dielectricbased CMOS inverter cell built using DG-MOSFET on channel thickness (T<sub>si</sub>) is also investigated in this work. The organization of this paper is as: The paper starts with an introduction as section 1 and the device description with the simulation setup is elaborated in section 2. Section 3 presents the design and analysis of the DG-MOSFET based CMOS inverter circuit. Finally, the conclusion is drawn in section 4.

## **MATERIALS AND METHODS**

The n/p-type double-gate (DG)-MOSFET structure is depicted in Fig. 1(a). 2D Sentaurus TCAD mixed-mode simulator [12] is used for simulating the DG-MOSFET. The channel thickness (T<sub>st</sub>) is speckled in the range of 6-14 nm for a fixed channel length (L<sub>a</sub>) and interfacial layer thickness (T<sub>i</sub>) of 30 nm and 0.2 nm respectively [13]. The Source/Drain doping concentration is set at 10<sup>20</sup> cm<sup>-3</sup> with arsenic (boron) for n-type (p-type). The channel region is uniformly doped with boron (arsenic) for n-type (p-type) at 1016 cm-3. The titanium oxide (TiO<sub>2</sub>) is used as high-K dielectric material (K = 40) for gate oxide to investigate the effect of the same on the performance of CMOS inverter [14]. The effective oxide thickness (EOT) is fixed at 1 nm throughout the study [15]. The physical thickness (T<sub>Phy</sub>) for the TiO<sub>2</sub> is calculated as per  $T_{phy} = \{(EOT - T_i) \times K/3.9\}$ . Table 1 tabulates the parameters used for the simulation of DG-MOSFET devices. Further, the Metal gate having a work function of 4.6 eV is utilized to dodge the poly-depletion effects [16].

Table 1. DG-MOSFET Parameter details.

| Parameters                      | Value                                     |

|---------------------------------|-------------------------------------------|

| Channel Length                  | 30 nm                                     |

| Interfacial Layer Thickness     | 0.2 nm                                    |

| EOT                             | 1 nm                                      |

| Gate Dielectric Constant (K)    | 40                                        |

| Source/Drain Doping             | 1×10 <sup>20</sup> atoms/cm <sup>-3</sup> |

| Channel Thickness (Tsi)         | 6-14 nm                                   |

| Lateral Straggle ( $\sigma_L$ ) | 1 nm                                      |

| Channel Doping                  | 1×10 <sup>16</sup> atoms/cm <sup>-3</sup> |

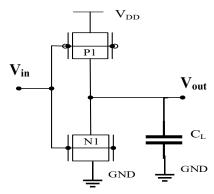

Fig. 2. DGMOSFET-based CMOS inverter circuit.

The saturation velocity ( $V_{sat}$ ) is set at 2.036 × 10<sup>7</sup> cm/s for the correct coupling of the carrier's transport phenomena [17-18]. A simulation study is executed using the following models: Philip unified mobility model, Lombardi mobility model, and band to band auger recombination, modified local density approximation (MLDA) quantization model to consider the quantum-mechanical effects in the device, old slotboom bandgap narrowing phenomenon, and SRH recombination/ generation model [19].  $I_D - V_{gs}$  characteristics of n/p - type DG-MOSFET are in good calibration with the experimental data presented in our earlier work [20] and are reproduced as shown in Fig. 1 (b). Further, it can be observed from Fig. 1(b) that high-k gate dielectric results in improved oncurrent  $(I_{on})$  but degrades the off-current  $(I_{off})$ .

# **RESULTS AND DISCUSSIONS**

Fig. 2 displays the schematic view of a complementary metal-oxide-semiconductor (CMOS) inverter cell. The CMOS inverter circuit

is executed with  $SiO_2$  (k = 3.9) and  $TiO_2$  (k = 40) based gate-stacked double-gate (DG)-MOSFET. The aspect ratio of p-type DG-MOSFET is made twice of n-type DG-MOSFET to match the current through both the transistors as can be verified from Fig. 1(b) [21].

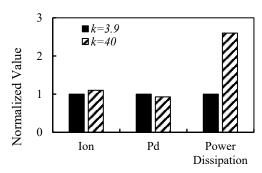

It is a renowned fact that the device performance for digital applications leans on the on-current ( $I_{on}$ ). Higher  $I_{on}$  will result in better delay performance [22]. Fig. 3 elucidates that the use of high-k dielectric as an alternative to  $SiO_2$  for gate oxide increases the on-current ( $I_{on}$ ), which can be attributed to improved delay performance of the CMOS inverter circuit. Furthermore, as observed in Fig 1(b), the high-k dielectric as gate oxide results in increased off current ( $I_{off}$ ). This is attributed to an increase in power dissipation for  $TiO_2$  based DG-MOSFET as compare to  $SiO_2$  based DG-MOSFET as shown in Fig. 3.

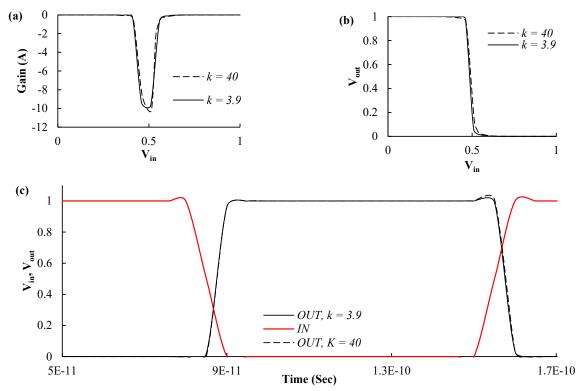

The transfer, gain, and transient characteristics of high-k gate dielectric DG-MOSFET based CMOS inverter for  ${\rm SiO_2}$  and  ${\rm TiO_2}$  as gate oxide is compared

Fig. 3. Comparison of  $I_{on}$ ,  $P_{d}$  and Power dissipation of DG-MOSFET built with SiO $_{2}$  & TiO $_{2}$  as a gate oxide.

Fig. 4. (a) Transfer characteristic (b) Gain Characteristic (c) Transient Characteristic of DGMOSFET-based CMOS Inverter Circuit.

in Fig. 4(a), Fig. 4(b) and Fig. 4(c) respectively. It is found that the low noise margin  $\mathrm{NM}_{\mathrm{L}}$  and high noise margin  $\mathrm{NM}_{\mathrm{H}}$  of the inverter circuit can be increased by using  $\mathrm{TiO}_{2}$  material as gate oxide which may be attributed to improved DIBL of pullup and pull-down transistor [23].

Further, large noise margins are not the only requirement. The regenerative property is another property that must be possessed by the inverter circuit to ensure that a distributed signal converges back to within the noise margins range after passing through several logical stages.

Inverter Gain (A) is the parameter that can be used to quantify the regenerative property and can be given by differentiating the output voltage (Vout) with respect to input voltage (Vin) i.e.

$$A = \frac{dV_{out}}{dV_{in}}$$

Higher the gain (A), the better will be the regenerative property [21]. Improvement is observed in the gain (A) of the DG-MOSFET based CMOS inverter circuit by using high-*k* gate dielectric as shown in Fig. 4(b). Thus, for DG-

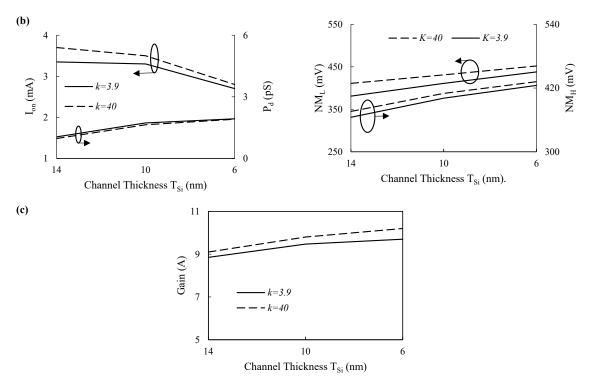

Fig. 5. (a) I<sub>20</sub> & P<sub>4</sub> v/s T<sub>51</sub> (b) NM<sub>4</sub> & NM<sub>4</sub> v/s T<sub>51</sub> (c) Gain (A) v/s T<sub>51</sub> for SiO<sub>2</sub> (k=3.9) & TiO<sub>2</sub> (k=40) as gate oxide.

MOSFET based CMOS inverter circuit, high-k gate dielectric-based devices are an attractive option. Furthermore, channel thickness ( $T_{\rm si}$ ) is among the vital parameters for MOS designing, which impacts the performance behavior of high-k gate dielectrics [16]. The comparative enhancement in performance metrics of DG-MOSFET based CMOS inverter circuit realized with  ${\rm TiO_2}$  as compare to  ${\rm SiO_2}$  as gate oxide for various channel thicknesses is explained in the following subsection.

## Channel Thickness (Ts.)

The simulative analysis of DG-MOSFET based CMOS inverter circuit realized with  $SiO_2/TiO_2$  as gate oxide collectively with channel thickness ( $T_{Si}$ ) is been carried out and conferred in this subsection. The on-current ( $I_{on}$ ) values of  $SiO_2$  (k=3.9) &  $TiO_2$  (k=40) gate oxide-based DG-MOSFET for various value of  $T_{Si}$  is plotted in Fig. 5(a). It is espied that, with downscaling of the  $T_{Si}$  the  $I_{on}$  value decreases resulting in deprivation in delay performance ( $P_{d}$ ) (Fig. 5(a)). Further, an improvement in low noise margin ( $NM_L$ ) and high noise margin ( $NM_H$ ) of the DG-MOSFET based CMOS inverter circuit is been observed with the scaling down of  $T_{Si}$ . The  $NM_L$  &  $NM_H$  for various values of  $T_{Si}$  is outlined in

Fig. 5 (b). It is noticed that inverter gain (A) also gets improved with downscaling of  $T_{si}$  (Fig. 5 (c)) which indicates that the inverter will show a better regenerative property at lower  $T_{si}$ .

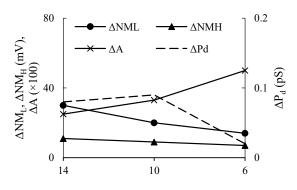

In our earlier work, we testified that the variation in channel thickness (Tsi) affects the outcome of the high-k gate dielectric on the performance of FinFET based 6T-SRAM cells [13]. Fascinatingly, it is espied that the variation in channel thickness (T<sub>si</sub>) also affects the outcome of the high-k gate dielectric on the performance of DG-MOSFET based CMOS inverter. In other words, change in performance metrics ( $\Delta F$  =  $F_{\kappa=40}$  -  $F_{\kappa=3.9}$ , where F is either  $P_d$ , A, or  $NM_L/NM_H$ ) of DG-MOSFET based CMOS inverter realized with TiO<sub>2</sub> as gate oxide as compared to CMOS inverter realized with SiO, as gate oxide is Tsi dependent. The improvement in propagation delay  $(P_d)$  increases from  $\sim 2$  % at  $T_{si} = 6$  nm to ~ 7 %  $T_{si}$  = 14 nm (Fig. 6). Furthermore, Fig. 6 elucidates that the change in Noise Margins i.e. ΔΝΜ, & ΔΝΜ,, increases with scaling up of T, (2% & 1% respectively at  $T_{si}$  = 6 nm and 7% & 10% respectively at T<sub>si</sub> =14 nm). However, the change in Gain ( $\Delta A$ ) decreases from 5% at  $T_{si}$  = 6 nm to 2% at  $T_{si} = 14$  nm.

Channel Thickness T<sub>Si</sub> (nm)

Fig. 6. ΔNM<sub>u</sub>, ΔNM<sub>u</sub>, ΔP<sub>d</sub> & ΔA for the various value of T<sub>s</sub>.

### CONCLUSION

The channel thickness dependency of DG-MOSFET based CMOS inverter circuit built using High-k gate dielectric material i.e.  $TiO_3$  (k = 40) has been explored through extensive device simulations. It is espied that the performance matrices i.e. noise margin, delay, and gain of the DG-MOSFET based CMOS inverter circuit show improvement when SiO<sub>2</sub> is replaced by a high-k dielectric material (TiO<sub>2</sub>) in the gate-stack configuration. It is also noticed that scaling down of channel thickness (T<sub>s</sub>) further improves the low & high noise margins (NM, & NM,), and gain (A) of the inverter circuit for both SiO, and TiO, gate dielectrics with negligible degradation in delay performance. However, the comparative improvement (ΔF) observed in performance matrices caused by high-k gate dielectric degrades with downscaling of channel thickness (Tsi) from 14 nm to 6 nm. It is also observed that ΔNM,  $\Delta NM_{H}$ , &  $\Delta P_{d}$  are aggravated from 7 %, 10 %, and 7 % respectively at  $T_{si}$  =14 nm to 2 %, 1 %, and 2 % respectively at  $T_{si}$  = 6. Accordingly, it is relevant to consider lower channel thickness (T<sub>si</sub> ~ 6 nm) when high-k gate dielectric-based DG-MOSFET is used for the designing of CMOS inverter circuit.

## **CONFLICT OF INTEREST**

The authors declare that they have no competing interests.

## REFERENCES

- Tayal S., Nandi A., (2018), Performance analysis of junctionless DG-MOSFET based 6T SRAM with gate-stack configuration. *Micro Nano Lett.* 13: 838-841.

- [2] Kuhn K. J., (2012), Consideration for ultimate CMOS scaling. *IEEE Trans. Electron Dev.* 59: 1813-1828.

- [3] Zhang W., Fossum J. G., Mathew L., Du Y., (2005), Physical

- insights regarding design and performance of independentgate FinFETs. *IEEE Trans. Electron Dev.* 52: 2198-2206.

- [4] Tayal S., Nandi A., (2017), Analog/RF performance analysis of inner gate engineered junctionless Si nanotube. Superlatt. Microst. 111: 862-871.

- [5] Interntional Technology Roadmap for Semiconductor (ITRS) for Radio Frequency and Analog/Mixed-signal Technologies. (2013), [Online]. Available: www.itrs.net.

- [6] Mohapatra N. R., Desai M. P., Narendra S. G., Rao V. R., (2002), The effect of high-K gate dielectrics on deep submicrometer CMOS device and circuit performance. *IEEE Trans. Electron Dev.* 49: 826-831.

- [7] Tayal S., Nandi A., (2017), Analog/RF performance analysis of channel engineered high-k gate-stack based junctionless trigate-FinFET. Superlatt. Microst. 112: 287-295.

- [8] Momose H. S., Ono M., Yoshitomi T., Ohguro T., Nakamura S. I., Saito M., Iwai H., (1996), 1.5 nm direct-tunneling gate oxide Si MOSFET's. IEEE Trans. Electron Dev. 43: 1233-1242.

- [9] Tayal S., Nandi A., (2017), Study of 6T SRAM cell using high-k gate dielectric based junctionless silicon nanotube FET. Superlatt. Microst. 112: 143-150.

- [10] Ribes G., Mitard J., Denais M., Bruyere S., Monsieur F., Parthasarathy C., Vincent E., Ghibaudo G., (2005), Review on high-K dielectrics reliability issues. *IEEE Trans. Dev. Mater. Reliab*. 5: 5-19.

- [11] Pradhan K. P., Mohapatra S. K., Sahu P. K., Behera D. K., (2014), Impact of high-K dielectric on analog and RF performance of nanoscale DGMOSFET, Microelectron. J. 45: 144-151.

- [12] Sentarus Device User Guide. [online]. Available: http://www.synopsys.com.

- [13] Tayal S., Nandi A., (2018), Effect of high-K gate dielectric inconjunction with channel parameters on the performance of FinFET based 6T SRAM. J. Nanoelectron. Optoelectron. 13: 768-774.

- [14] Tayal S., Nandi A., (2018), Interfacial layer dependence of high-k gate stack based conventional trigate FinFET concerning analog/RF performance, in Proc. of 4<sup>th</sup> International Conf. on Devices, Circuits and Systems (ICDCS), 305-308.

- [15] Tayal S., Nandi A., (2017), Comparative analysis of high-k gate stack based conventional & junctionless FinFET, in Proc. of 14<sup>th</sup> IEEE India Council International Conf. (INDICON), 1-4.

- [16] Tayal S., Nandi A., (2017), Effect of FIBL in-conjunction

- with channel parameters on analog and RF FOM of FinFET. *Superlatt. Microst.* 105: 152-162.

- [17] Granzner R., Polyakov V. M., Schwierz F., Kittler M., Doll T., (2003), On the suitability of DD and HD models for the simulation of nanometer double-gate MOSFETs. *Phys. E.* 19: 33-38.

- [18] Nandi A., Saxena A. K., Dasgupta S., (2016), Oxide thickness and S/D junction depth based variation aware OTA design using underlap FinFET. *Microelectron. J.* 55: 19-25.

- [19] Tayal S., Nandi A., (2018), Optimization of gate stack in junctionless Si-nanotube FET for analog/RF applications. *Mater Sci Semicond. Process*. 80: 63-67.

- [20] Gupta S., Nandi A., (2019), Effect of air spacer in underlap GAA nanowire: An analog/RF prospective, IET Circ Devices Syst. 13: 1196-1202.

- [21] Rabey J. M., Chandrakasan A. P., Nikolic B., (2003), Digital integrated circuits: A Design Perspective, Pearson Education.

- [22] Sachid A. B., Manoj C. R., Sharma D. K., (2008), Gate fringeinduced barrier lowering in underlap FinFET structures and its optimization. *IEEE Electron Dev. Lett.* 29: 128-130.

- [23] Saini G., Choudhary S., (2016), Improving the performance of SRAMs using asymmetric junctionless accumulation mode (JAM) FinFETs. *Microelectron. J.* 58: 1-8.